# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2016

# Just In Time Assembly (JITA) - A Run Time Interpretation Approach for Achieving Productivity of Creating Custom Accelerators in FPGAs

Sen Ma University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the Computer and Systems Architecture Commons, Programming Languages and Compilers Commons, and the Software Engineering Commons

#### Recommended Citation

Ma, Sen, "Just In Time Assembly (JITA) - A Run Time Interpretation Approach for Achieving Productivity of Creating Custom Accelerators in FPGAs" (2016). *Theses and Dissertations*. 1810. http://scholarworks.uark.edu/etd/1810

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

# Just In Time Assembly (JITA) - A Run Time Interpretation Approach for Achieving Productivity of Creating Custom Accelerators in FPGAs

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering

by

Sen Ma

Capital Normal University

Bachelor of Science in Computer Engineering, 2007

Capital Normal University

Master of Science in Computer Engineering, 2010

# December 2016 University of Arkansas

| This dissertation is approved for reco | ommendation to the Graduate Council |  |

|----------------------------------------|-------------------------------------|--|

|                                        |                                     |  |

| Dr. David Andrews                      |                                     |  |

| Dissertation Director                  |                                     |  |

| Dr. Christophe Bobda                   |                                     |  |

| Committee Member                       |                                     |  |

| D. I.I. C. I                           | D. W. Ol.                           |  |

| Dr. John Gauch                         | Dr. Xuan Shi                        |  |

| Committee Member                       | Committee Member                    |  |

#### **Abstract**

The reconfigurable computing community has yet to be successful in allowing programmers to access FPGAs through traditional software development flows. Existing barriers that prevent programmers from using FPGAs include: 1) knowledge of hardware programming models, 2) the need to work within the vendor specific CAD tools, 3) and the requirement to pass each design through synthesis, place and route.

This thesis presents a series of published papers that explore different aspects of a new approach being developed to remove the three barriers and enable programmers to compile accelerators on next generation reconfigurable manycore architectures. The approach is entitled Just In Time Assembly (JITA) of hardware accelerators. The approach has been defined to allow hardware accelerators to be built and run through software compilation and run time interpretation outside of CAD tools and without requiring each new accelerator to be synthesized. The approach advocates the use of libraries of pre-synthesized components that can be referenced through symbolic links in a similar fashion to dynamically linked software libraries. Synthesis still must occur but is moved out of the application programmers software flow and into the initial coding process that occurs when programming patterns that define a Domain Specific Language (DSL) are first coded. Programmers see no difference between creating software or hardware functionality when using the DSL. A new run time interpreter is introduced to assemble the individual pre synthesized hardware accelerators that comprise the accelerator functionality within a configurable tile array of partially reconfigurable slots at run time. Qualitative results are presented that demonstrate how software programmers can create hardware accelerators without deviating from their traditional software practices. Quantitative results are presented that compares utilization, performance, and productivity of the approach to what would be achieved by full custom accelerators created through traditional CAD flows using hardware programming models and passing through synthesis.

©2016 by Sen Ma All Rights Reserved

# Acknowledgements

I would like to extend my thanks to my thesis committee, especially my advisor Dr. David Andrews for providing me the oppertunities to finish my research. I would also like to thank my parents for their support and encouragement.

# **Contents**

| 1  | Intr       | oduction                                                         | 1  |

|----|------------|------------------------------------------------------------------|----|

|    | 1.1        | Hardware Design Skills                                           | 2  |

|    | 1.2        | Use of Vendor Specific CAD Tools and Synthesis                   | 4  |

|    | 1.3        | Objective                                                        | 5  |

|    | 1.4        | Thesis Contributions                                             | 6  |

|    | 1.5        | Dissertation Organization                                        | 7  |

|    |            |                                                                  | ·  |

| Re | eferen     | ces                                                              | 8  |

| 2  | A R        | un Time Interpretation Approach For Creating Custom Accelerators | 12 |

|    | 2.1        | Introduction                                                     | 12 |

|    | 2.2        | Approach                                                         | 14 |

|    |            | 2.2.1 Example                                                    | 16 |

|    |            | 2.2.2 Run Time Interpreter                                       | 16 |

|    | 2.3        | Experimental Results and Analysis                                | 18 |

|    |            | 2.3.1 Productivity Analysis                                      | 19 |

|    |            |                                                                  | 22 |

|    | 2.4        | •                                                                | 23 |

|    | 2.5        |                                                                  | 24 |

| Re | eferen     | aces                                                             | 25 |

| _  | <b>.</b> . |                                                                  |    |

| 3  |            | In Time Assembly of Accelerators                                 | 26 |

|    | 3.1        |                                                                  | 26 |

|    |            |                                                                  | 29 |

|    | 3.2        | Intermediate Fabric                                              | 30 |

|    |            |                                                                  | 31 |

|    |            | $\epsilon$                                                       | 31 |

|    |            | •                                                                | 33 |

|    | 3.3        |                                                                  | 34 |

|    | 3.4        | 1                                                                | 35 |

|    | 3.5        | Experimentation and Analysis                                     | 37 |

|    |            | 3.5.1 Creating the Accelerators                                  | 38 |

|    |            | 3.5.2 Discussion: Programmer Accessibility                       | 39 |

|    |            | 3.5.3 Discussion: Performance Analysis                           | 41 |

|    | 3.6        | Conclusion                                                       | 42 |

| Re | eferen     | ices                                                             | 44 |

| 4  | Dun        | Time Interpretation for Creating Custom Accelerators             | 45 |

| 7  | 4.1        | Introduction                                                     | 45 |

|    | 4.1        | 4.1.1 Overview of Approach                                       | 43 |

|    |            | 4.1.1 Overview of Approach                                       | +/ |

|    | 4.2    | Overlay                                                                    |            |

|----|--------|----------------------------------------------------------------------------|------------|

|    |        | 4.2.1 PR Tiles                                                             |            |

|    |        | 4.2.2 Programmable Switch                                                  |            |

|    | 4.0    | 4.2.3 Local Memory                                                         |            |

|    | 4.3    | Interpreter                                                                |            |

|    | 4.4    | Interpreter Functionality                                                  |            |

|    | 4.5    | Experimental Results and Analysis                                          |            |

|    |        | 4.5.1 Creating the Accelerators                                            |            |

|    |        | 4.5.2 Discussion: Performance Analysis                                     |            |

|    | 4.6    | Conclusion                                                                 | . 61       |

| Re | eferen | ices                                                                       | 63         |

| 5  | Bree   | eze Computing: A Just In Time Approach for Virtualizing FPGAs in the Cloud | 65         |

|    | 5.1    | Introduction                                                               | . 65       |

|    |        | 5.1.1 Contributions                                                        | . 69       |

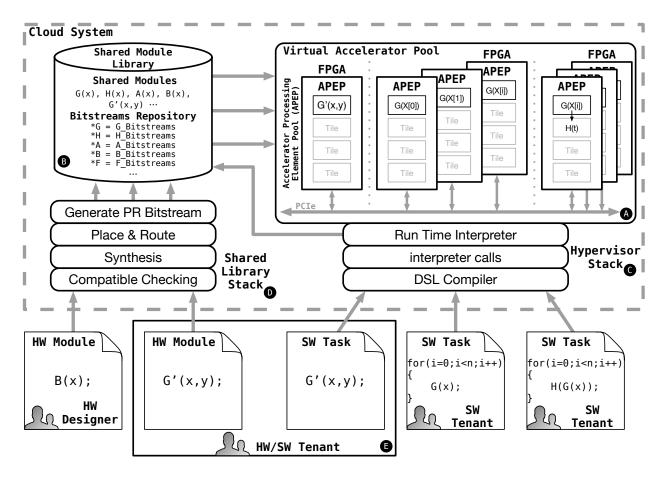

|    | 5.2    | User Front End                                                             | . 70       |

|    | 5.3    | Virtualization Architecture                                                | . 72       |

|    |        | 5.3.1 Local Memory                                                         | . 74       |

|    | 5.4    | Run Time Interpreter                                                       | . 75       |

|    | 5.5    | Experimental Results and Analysis                                          | . 76       |

|    |        | 5.5.1 Discussion: Programmer Accessibility to FPGAs                        | . 79       |

|    |        | 5.5.2 Discussion: Scalability                                              | . 79       |

|    |        | 5.5.3 Discussion: Virtualization for Multiple Threads                      | . 81       |

|    | 5.6    | Conclusion                                                                 | . 82       |

| Re | eferen | ices                                                                       | 83         |

| 6  | Arcl   | hborn: A Custom Multiprocessor Architecture Generation Framework for Plat  | t <b>-</b> |

|    |        | n FPGAs                                                                    | 84         |

|    | 6.1    | Introduction                                                               | . 84       |

|    | 6.2    | Background and Related Work                                                |            |

|    | 6.3    | Archborn Framework                                                         |            |

|    |        | 6.3.1 Archborn APIs                                                        |            |

|    |        | 6.3.2 Archborn Templates                                                   |            |

|    | 6.4    | Hardware Platforms with Programming Models                                 |            |

|    | ٠      | 6.4.1 Targeted Programming Models                                          |            |

|    |        | 6.4.2 Design Flow with Archborn                                            |            |

|    |        | 6.4.3 Experimental Results                                                 |            |

|    | 6.5    | Conclusion                                                                 |            |

| Re | eferen | ices                                                                       | 101        |

| 7  |        | clusion                                                                    | 102        |

| ′  | Con    | 7.0.1 Summary                                                              |            |

|    | 7 1    | Future Work                                                                | 102        |

# **List of Figures**

| 1.1<br>1.2                                           | Intel Reconfigurable Manycore and QPI Interconnect                                                                                                                                                                                                                                                                                                                                                  |                                  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4                             | Design Flow of Matrix Multiplication Accelerator.  Compiler Flow and VAM Call Generation.  3 × 3 Tile Array and Interconnect Network.  Speedup of Benchmarks.                                                                                                                                                                                                                                       | 17<br>20                         |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6               | Design Flow.  3 × 3 Tile Array and Interconnect Network.  Switch Routing.  Design Portability with JIT.  Interpreter Calls For Inner Product.  Speedup of Benchmarks.                                                                                                                                                                                                                               | 32<br>33<br>36<br>37             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5                      | Design Portability with JIT.  DSL Programming Patterns [7].  3 × 3 Tile Array and Interconnect Network.  Switch Routing.  VAM Call Flow With Different Cases.                                                                                                                                                                                                                                       | 49<br>52<br>54                   |

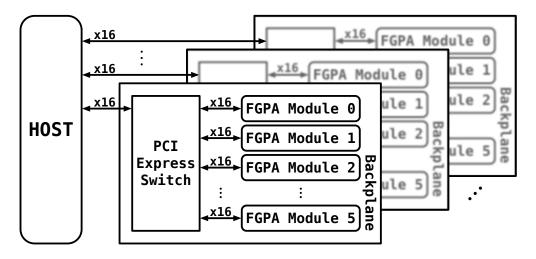

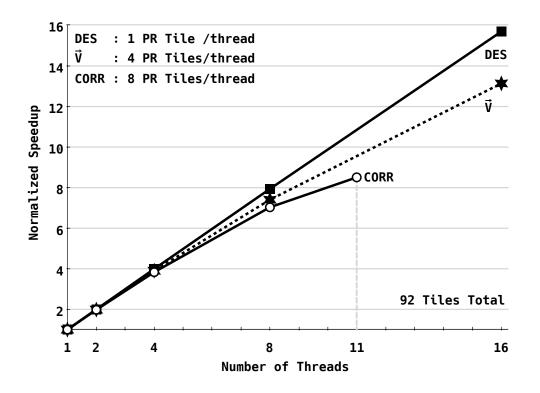

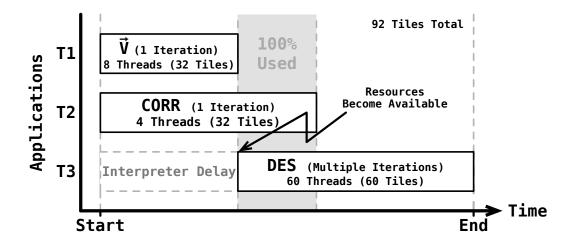

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8 | Multiple Tasks Mapping on Cloud System Through Run Time Interpreter.  Design Flow.  Architecture of accelerator processing element pool (APEP).  VAM Call Flow With Different Cases.  Block Diagram of Micron's Architecture [9].  Mapping three benchmarks on APEP.  Scalability of the Overlay.  Simultaneously Sharing the Cloud Computing System with JIT approach among multiple applications. | 70<br>73<br>74<br>77<br>80<br>81 |

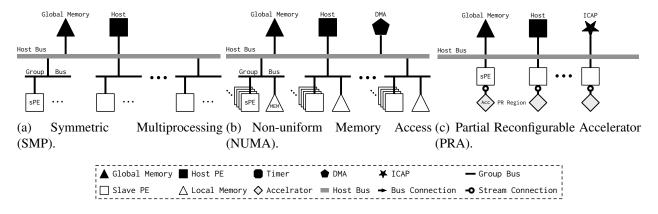

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6               | MHS Descriptions and TCL Commands                                                                                                                                                                                                                                                                                                                                                                   |                                  |

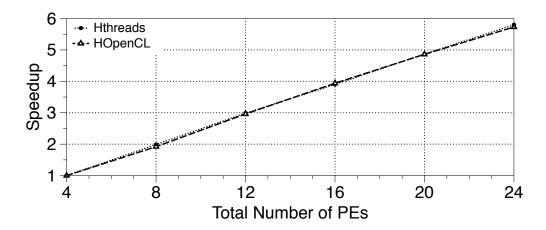

| 6.7<br>6.8                                           | Hardware Platforms with Programming Models Generated by Archborn Templates. Evaluation of Scalability With Various PEs                                                                                                                                                                                                                                                                              | 97<br>100                        |

# **List of Tables**

| 1.1 | Utilization and synthesis time of MPSoC with various PEs                  |

|-----|---------------------------------------------------------------------------|

| 2.1 | Code Complexity                                                           |

| 2.2 | productivity                                                              |

| 3.1 | Code Complexity                                                           |

| 3.2 | Prototype Programming Patterns                                            |

| 3.3 | productivity                                                              |

| 3.4 | Resource utilization on Virtex7                                           |

| 4.1 | VAM Calls                                                                 |

| 4.2 | Pre-Synthesized Parallel Pattern Samples                                  |

| 4.3 | Performance                                                               |

| 5.1 | Utilization of Resource for Applications                                  |

| 6.1 | Archborn APIs and Templates                                               |

| 6.2 | Resource Utilization of Hthreads and HOpenCL Platforms With Various PEs 9 |

### **List of Published Papers**

This dissertation is based on the following five papers:

- Chapter 2 A Run Time Interpretation Approach For Creating Custom Accelerators

Sen Ma, Zeyad Aklah, and David Andrews

In Proceedings of the Conference on Field-Programmable Logic and Applications

(FPL), Sep. 2015, London, UK.

- Chapter 3 Just In Time Assembly of Accelerators

Sen Ma, Zeyad Aklah, and David Andrews

In Proceedings of the Conference on 24th ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA), Feb. 2016, Monterey, CA, USA.

- Chapter 4 Run Time Interpretation for Creating Custom Accelerators

Sen Ma, Zeyad Aklah, and David Andrews

In Proceedings of the Conference on Design, Automation and Test in Europe

(DATE), MAR. 2016, ICC, Dresden, Germany.

- Chapter 5 Breeze Computing: A Just In Time Approach for Virtualizing FPGAs in the Cloud

Sen Ma, David Andrews, Shanyuan Gao, and Jaime Cummins

In Proceedings of the Conference on Reconfigurable Computing and FPGAs

(ReConfig), Nov. 2016, Cancun, Mexico.

- Chapter 6 Archborn: A Custom Multiprocessor Architecture Generation Framework for Platform FPGAs

Sen Ma, Hongyuan Ding, Miaoqing Huang, and David Andrews

In Proceedings of the Conference on Reconfigurable Computing and FPGAs

(ReConfig), Dec. 2015, Riviera Maya, Mexico.

### Chapter 1

#### Introduction

We are facing a new era where power and energy efficiency have become first-class design constraints within data center architectures. The Computing Research Association (CRA) working group report, entitled "Revitalizing Computer Architecture Research", deemed this as a grand challenge problem in their "System 2020 Vision". They put forth the challenge of creating a new featherweight supercomputer architecture that can achieve 0.001 nJ/op [1]. This is four orders of magnitude improvement over today's systems. Reconfigurable manycores are one approach that our semiconductor industry is pursuing towards meeting this challenge [2, 3, 4].

Reconfigurable manycores are a new hybrid architecture that include a Field Programmable Gate Array (FPGA) as a coprocessor along with a traditional general purpose manycore chip. The FPGA offers the advantage that it that can be reconfigured on an application-by-application basis within the data center. The hope is the FPGA will be able to exploit, in an energy-efficient manner, the irregular types of parallelism that exists throughout emerging big data analytics and machine learning algorithms [5, 6, 7, 8, 9, 10]. Microsoft validated the energy and performance benefits of integrating FPGAs into data centers. They created an experimental server system called Catapult that allowed their document ranking algorithms to be offloaded into sets of FPGAs connected to standard Intel manycore processors. Using FPGAs allowed them to double the performance of their Bing search engine, but at only a 30% increase in energy [3].

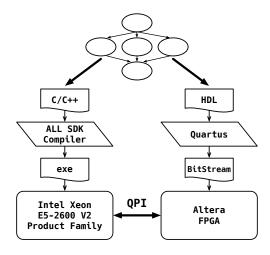

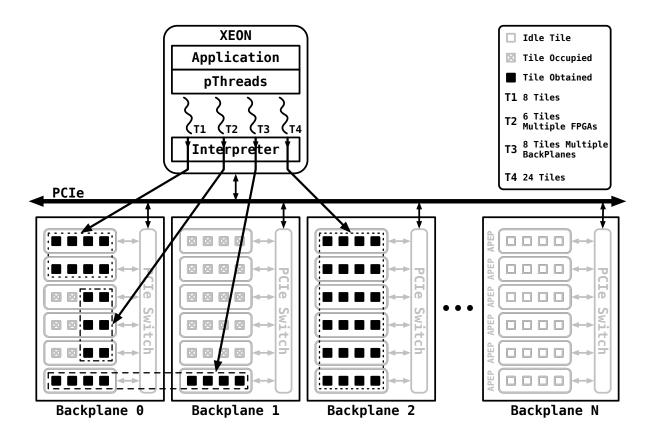

There are two problems that will prevent widespread deployment of reconfigurable manycores throughout data centers from being successful. First designing and placing circuits within FPGAs requires hardware design skills. Second designs must be synthesized within Computer Aided Design (CAD) hardware design flows. This is represented in the top right of Figure 1.1. These problems are non-starters for successful deployment throughout our software

Figure 1.1: Intel Reconfigurable Manycore and QPI Interconnect.

based technology sectors. The United States Bureau of Labor Statistics reports that over 1.3M software programmers and only 85,000 hardware designers are employed within the United States [11]. This is the issue; we simply do not educate and employ sufficient numbers of hardware designers to support the coming broad deployment of these reconfigurable manycores.

#### 1.1 Hardware Design Skills

Lack of programmer accessibility is continually called out as the biggest fundamental difficulty in taking reconfigurable computing mainstream [12]. This issue was a catalyst for the latest generation of High Level Synthesis [13]. HLS approaches start with a limited set of the C language statements and add additional constructs or pragmas to expose parallelism and guide synthesis [14, 15, 16, 17, 18, 19, 20, 21, 22, 23]. HLS and the use of imperative languages is no Panacea [24]. Generating efficient parallel circuits from sequential languages remains challenging, and does not remove the burden for programmers to study the chips underlying hardware structures. Although it is fairly easy to generate an inefficient circuit from HLS, significant effort is required to make the requisite low level platform specific optimizations to synthesize efficient circuits. Recently FPGA vendors have been working on bringing FPGAs under modern software heterogeneous programming frameworks [25, 26, 27]. These higher level

```

2 #define ChunkSize (sizeof(MPort)/sizeof(int))

3 #define LoopCount (512/ChunkSize)

4 //Maximize data width from memory

5 void(MPort *mem) {

//Use a local buffer and burst access

MPort buff[LoopCount];

memcpy(buff, mem, LoopCount);

1 void(int *mem) {

//Use a local variable for accumulation

mem[512]=0;

int sum=0;

3

for(int i=0; i<512; i++) {</pre>

11

for(int i=0; i<LoopCount; i++) {</pre>

mem[512] += mem[i];

//Use additional directives

5

}

13

//e.g. pipeline and unroll for parallel exec.

6 }

#pragma PIPELINE

(a) Unoptimized: Exec. Time = 27,236 clock cycles.

15

for(int j=0; j<ChunkSize; j++) {</pre>

16

#pragma UNROLL

17

sum+=(int)(buff[i]>>j*sizeof(int)*8);

18

19

20

mem [512] = sum;

21

```

1 //Width of MPort = 16 \* sizeof(int)

(b) Optimized: Exec. Time = 302 clock cycles.

Figure 1.2: Comparing optimized HLS and unoptimized HLS from [28].

frameworks still use HLS underneath to then create the hardware accelerators.

Generating circuits from declarative languages has also been popular [29, 30, 31, 32, 33, 34, 35, 36, 37]. Advocates argue that declarative languages provide a better starting model of concurrency for generating parallel gates compared to HLS. Despite these articulated advantages and continued interest by researchers, declarative languages have not achieved a level competitiveness with HLS within industry.

Researchers within reconfigurable computing are acknowledging the acceptance of Domain Specific Langauges (DSLs) within the software community. DSLs in general provide a restricted set of programming patterns relevant to a particular domain. DSLs such as MATLAB, SQL, Snort, Perl, and Hadoop are commonplace within our software industry. The reconfigurable

computing community is increasingly investigating DSLs as front end alternatives to HLS for programming FPGAs [38, 39, 40]. DSLs are used as another layer of abstraction between the programmer and the underlying HLS tools.

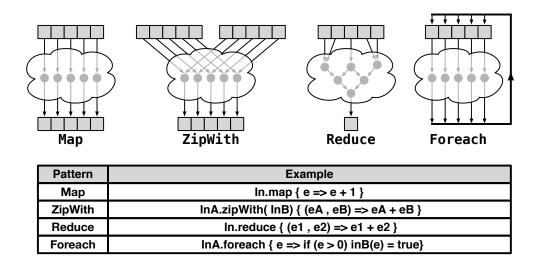

The bodies of the software programming patterns still need to transformed with pragmas based on platform specific knowledge as shown in Figure 1.2. HLS tools are entirely appropriate to transform the bodies of the patterns into synthesizeable code. However starting from a DSL allows this lower level coding to be performed once by an experienced hardware designer and then reused by all application programmers. George et. al. [40, 41] showed the benefit of this approach using programming patterns from OptiML, a DSL for machine learning [42]. Figure 4.2 shows the key OptiML programming patterns that were combined and synthesized.

## 1.2 Use of Vendor Specific CAD Tools and Synthesis

The second issue that will block the widespread deployment of reconfigurable manycore system throughout our data centers and software based technology sectors is the use of CAD tools and synthesis. CAD tools are provided by FPGA vendors and are not interoperable. Essentially Xilinx CAD tools do not support Altera's FPGA architectures and vice versa. This represents a challenge for creating portable and reusable designs. CAD tools used for designing and programming today's FPGAs have a direct heritage to earlier VLSI hardware design tools. In general, CAD tools reinforce the notion that optimizing peak performance is an immutable first class design constraint when creating hardware circuits. Some research has been reported on how to soften the requirement of optimizing performance to achieve better designer productivity within earlier versions of vendor proprietary CAD tool flows [43, 44]. However newer versions of the Vendor tools remove this type of circumvention. What still remains true is that CAD tools integrate the steps of synthesis, place, and route within the design flow for creating hardware circuits.

Besides the use of CAD tools, designers also need to tolerate the increasingly time-consuming hardware synthesis process. The hardware synthesis process can breakdown to

| #PEs  | Utilization     |                | Hardware Synthesis Time (Min) |               |            |

|-------|-----------------|----------------|-------------------------------|---------------|------------|

| π1 L3 | LUTs            | BRAM           | Synthesis                     | Place & Route | Total Time |

| 1     | 25,009 ( 8.0%)  | 36.0 (3.5%)    | 25.5                          | 10.0          | 35.5       |

| 2     | 28,919 ( 9.5%)  | 45.5 (4.4%)    | 33.0                          | 11.0          | 44.0       |

| 4     | 35,449 (11.7%)  | 65.5 (6.4%)    | 50.8                          | 13.6          | 64.4       |

| 8     | 49,328 (16.3%)  | 105.5 (10.2%)  | 79.6                          | 16.5          | 96.1       |

| 16    | 76,926 (25.3%)  | 185.5 (18.0%)  | 159.2                         | 22.4          | 181.6      |

| 32    | 132,274 (43.6%) | 345.5 (33.54%) | 379.1                         | 64.5          | 443.6      |

| 64    | 240,778 (79.3%) | 665.5 (64.61%) | 1257.8                        | 110.5         | 1368.3     |

Table 1.1: Utilization and synthesis time of MPSoC with various PEs.

several steps: synthesis, placing, routing, and generating bitstreams. Table 1.1 shows the utilization and hardware synthesis time of six typical MPSoC system with different numbers of processing elements (PEs). The hardware synthesis time increases sharply following the growth of number of PEs. If any modification happens in the design, the designer have to suffer hourly re-synthesis process, which consequently complicates debugging and verification, reduces turns per day, and prevents FPGA from widespread deployment.

#### 1.3 Objective

It is important to remove the use of CAD tools and hardware synthesis from programmers design path. This can be addressed by exploiting:

- High level programming model abstraction: to allow programmers to design accelerator without the knowledge of hardware.

- Run time interpreter: to avoid the hardware synthesis, and to interpret the intermediate representation to the executable assemblies.

- Overlay design: to abstract the FPGA resource to run the executable assemblies during the runtime.

The objective of this dissertation is to demonstrate the feasibility of just in time assembly

(JITA) approach for software programmers to design accelerator without the using of CAD tools and hardware synthesis.

#### 1.4 Thesis Contributions

Throughout exploration of this work, I have made the following set of contributions and have published my findings in the conferences referenced for each contribution.

- *Run Time Interpreter* We created a C implementation of the interpreter. The interpreter dynamically places and routes the programming patterns within different configurations of the overlay (In Chapter 2 [45]).

- *Partial Reconfigurable Tile Overlay* We created a new overlay that uses partial reconfiguration tiles within a word width 2D switch or 1D crossbar interconnection. We provided a scripting tool to automatically create different configurations of the overlay for a DSL and FPGA (In Chapter 3 [46], 4 [47]).

- *Platform Independent Interpreter Language* We created a set of platform independent interpreter calls that enable portability over different overlays. This represents a separation of policy from a mechanism that allows a single set of interpreter calls to be implemented by all platform specific interpreters managing different overlays (In Chapter 5 [48]).

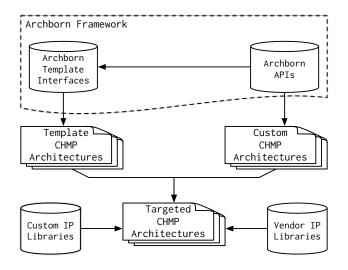

- Automated Overlay Generator We provided an open-source overlay architecture generation tool based on TCL scripts on FPGAs, to unify different overlay topology with various programming models for rapid system generation (In Chapter 6 [49]).

During the course of my studies, I also investigated and published additional work in support of my contributions. The work includes memory hierarchy [50], energy efficiency [51], and automate generation tools [52] in the MPSoC system.

# 1.5 Dissertation Organization

The remainder of this dissertation is organized as follows. Chapter 2 presents a prototype implemented by using the proposed design flow to address productivity issues of accelerator design in FPGA. Next, Chapter 3 focuses on the main design methodology of JITA for programmers to design accelerator in FPGA. The following Chapter 4, 5, 6 provides a detailed discussion of the proposed approach in this thesis to explore the trade-off among the productivity, utilization, and performance. Finally, Chapter 7 concludes the thesis and offers some potential future work that can follow this thesis.

#### References

- [1] CRA. Revitalizing Computer Architecture Research.

- [2] David Sheffield. IvyTown Xeon + FPGA: The HARP Program.

- [3] E. Chung D. Chiou K. Constantinides J. Demme H. Esmaeilzadeh J. Fowers G. Gopal J. Gray M. Haselman S. Hauck S. Heil A. Hormati J. Kim S. Lanka J. Larus E. Peterson S. Pope A. Smith J. Thong P. Xiao A. Putnam, A. Caulfield and D. Burger. A reconfigurable fabric for accelerating large-scale datacenter services. In 2014 ACM/IEEE 41st International Symposium on Computer Architecture (ISCA), pages 13–24, June 2014.

- [4] A. Caulfield E. Chung O. Firestein M. Haselman S. Heil K. Holohan M. Humphrey T. Juhasz P. Kaur S. Lanka D. Lo T. Massengill K. Ovtcharov M. Papamichael A. Putnam R. Seera R. Tadros J. Thong L. Woods D. Chiou D. Burger S. Alkalay, H. Angepat. Agile co-design for a reconfigurable datacenter. In *Proceedings of the 2016 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays*, FPGA '16, pages 15–15, New York, NY, USA, 2016. ACM.

- [5] S. Yao K. Guo B. Li E. Zhou J. Yu T. Tang N. Xu S. Song Y. Wang J. Qiu, J. Wang and H. Yang. Going deeper with embedded fpga platform for convolutional neural network. In *Proceedings of the 2016 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays*, FPGA '16, pages 26–35, New York, NY, USA, 2016. ACM.

- [6] E. Ghasemi and P. Chow. Accelerating apache spark big data analysis with fpgas. In 2016 IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), pages 94–94, May 2016.

- [7] Z. Istvn, D. Sidler, and G. Alonso. Runtime parameterizable regular expression operators for databases. In 2016 IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), pages 204–211, May 2016.

- [8] R. Chen and V. K. Prasanna. Accelerating equi-join on a cpu-fpga heterogeneous platform. In 2016 IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), pages 212–219, May 2016.

- [9] Joo-Young Kim Jeremy Fowers Karin Strauss Eric Chung Kalin Ovtcharov, Olatunji Ruwase. Accelerating deep convolutional neural networks using specialized hardware, February 2015.

- [10] M. Lavasani, H. Angepat, and D. Chiou. An fpga-based in-line accelerator for memcached. *IEEE Computer Architecture Letters*, 13(2):57–60, July 2014.

- [11] http://www.bls.gov/ooh/Computer-and Information-Technology/. Occupational Outlook Handbook.

- [12] David F. Bacon, Rodric Rabbah, and Sunil Shukla. Fpga programming for the masses. *Commun. ACM*, 56(4):56–63, April 2013.

- [13] Grant Martin and Gary Smith. High-level synthesis: Past, present, and future. *IEEE Design & Test of Computers*, 26(4):18–25, 2009.

- [14] Maya Gokhale and Ron Minnich. FPGA Computing in a Data Parallel C. In *Proceedings of the IEEE Workshop on FPGAs for Custom Computing Machines*, pages 94–101, 1994.

- [15] Optimized Generation of Data-Path from C Codes, March 2005.

- [16] N. Wirth. Hardware compilation: translating programs into circuits. *Computer*, 31(6):25–31, Jun 1998.

- [17] Michael Fingeroff. High-Level Synthesis Blue Book. Xlibris Corporation, 2010.

- [18] Walid A. Najjar, Wim Bohm, Bruce A. Draper, Jeff Hammes, Robert Rinker, J. Ross Beveridge, Monica Chawathe, and Charles Ross. High-Level Language Abstraction for Reconfigurable Computing. In *IEEE Computer*, pages 63–69, August 2003.

- [19] www.impulsec.com. ImpulseC. Last accessed December 7, 2016.

- [20] www.celoxica.com. Celoxica. Last accessed December 7, 2016.

- [21] Vivado High-Level Synthesis. www.xilinx.com/products/design-tools/vivado/integration/esl-design.html. Last accessed December 7, 2016.

- [22] M. Wazlowski, L. Agarwal, T. Lee, A. Smith, E. Lam, P. Athanas, H. Silverman, and S. Ghosh. PRISM-II Compiler and Architecture. In *Proceedings of the IEEE Workshop on FPGAs for Custom Computing Machines*, pages 9–16, 1993.

- [23] S. Gupta, N.D. Dutt, R.K. Gupta, and A. Nicolau. SPARK: A High-Level Synthesis Framework For Applying Parallelizing Compiler Transformations. In *International Conference on VLSI Design*, pages 461–466, January 2003.

- [24] Stephen A. Edwards. The Challenges of Synthesizing Hardware from C-Like Languages. *IEEE Design and Test of Computers*, 23(5):375–386, 2006.

- [25] T.S. Czajkowski, U. Aydonat, D. Denisenko, J. Freeman, M. Kinsner, D. Neto, J. Wong, P. Yiannacouras, and D.P. Singh. From opencl to high-performance hardware on fpgas. In *Field Programmable Logic and Applications (FPL), 2012 22nd International Conference on*, pages 531–534, Aug 2012.

- [26] M. Owaida, N. Bellas, K. Daloukas, and C.D. Antonopoulos. Synthesis of platform architectures from opencl programs. In *Field-Programmable Custom Computing Machines* (FCCM), 2011 IEEE 19th Annual International Symposium on, pages 186–193, May 2011.

- [27] A. Papakonstantinou, K. Gururaj, J.A. Stratton, Deming Chen, J. Cong, and W.-M.W. Hwu. Fcuda: Enabling efficient compilation of cuda kernels onto fpgas. In *Application Specific Processors*, 2009. SASP '09. IEEE 7th Symposium on, pages 35–42, July 2009.

- [28] N. George, Hyoukjoong Lee, D. Novo, T. Rompf, K.J. Brown, A.K. Sujeeth, M. Odersky, K. Olukotun, and P. Ienne. Hardware system synthesis from domain-specific languages. In

- Field Programmable Logic and Applications (FPL), 2014 24th International Conference on, pages 1–8, Sept 2014.

- [29] David Bacon, Rodric Rabbah, and Sunil Shukla. Fpga programming for the masses. *Queue*, 11(2):40:40–40:52, February 2013.

- [30] Rishiyur Nikhil. Bluespec system verilog: efficient, correct rtl from high level specifications. In *Formal Methods and Models for Co-Design*, 2004. MEMOCODE '04. Proceedings. Second ACM and IEEE International Conference on, pages 69–70, June 2004.

- [31] J. Bachrach, Huy Vo, B. Richards, Yunsup Lee, A. Waterman, R. Avizienis, J. Wawrzynek, and K. Asanovic. Chisel: Constructing hardware in a scala embedded language. In *Design Automation Conference (DAC)*, 2012 49th ACM/EDAC/IEEE, pages 1212–1221, June 2012.

- [32] Per Bjesse, Koen Claessen, Mary Sheeran, and Satnam Singh. Lava: Hardware design in haskell. In *Proceedings of the Third ACM SIGPLAN International Conference on Functional Programming*, ICFP '98, pages 174–184, New York, NY, USA, 1998. ACM.

- [33] Mary Sheeran. mufp, a language for vlsi design. In *Proceedings of the 1984 ACM Symposium on LISP and Functional Programming*, LFP '84, pages 104–112, New York, NY, USA, 1984. ACM.

- [34] Geraint Jones and Mary Sheeran. Circuit design in ruby. *Formal methods for VLSI design*, 1, 1990.

- [35] Andy Gill. Domain-specific languages and code synthesis using haskell. *Queue*, 12(4):30:30–30:43, April 2014.

- [36] David Greaves and Satnam Singh. Exploiting System-Level Concurrency Abstractions for Hardware Descriptions. *ACM Transactions on Reconfigurable Technology and Systems*, 5(N):1 thru 29, October 2008.

- [37] R. Wester, C. P. R. Baaij, and J. Kuper. A two step hardware design method using cλash. In 22nd International Conference on Field Programmable Logic and Applications, FPL 2012, Oslo, Norway, pages 181–188, USA, August 2012. IEEE Computer Society.

- [38] Gordon J. Brebner and Weirong Jiang. High-speed packet processing using reconfigurable computing. *IEEE Micro*, 34(1):8–18, 2014.

- [39] Peter Milder, Franz Franchetti, James C. Hoe, and Markus Püschel. Computer generation of hardware for linear digital signal processing transforms. *ACM Trans. Des. Autom. Electron. Syst.*, 17(2):15:1–15:33, April 2012.

- [40] N. George, Hyoukjoong Lee, D. Novo, T. Rompf, K.J. Brown, A.K. Sujeeth, M. Odersky, K. Olukotun, and P. Ienne. Hardware system synthesis from domain-specific languages. In Field Programmable Logic and Applications (FPL), 2014 24th International Conference on, pages 1–8, Sept 2014.

- [41] N. George, H. Lee, D. Novo, M. Owaida, D. Andrews, K. Olukotun, and P. Ienne. Automatic support for multi-module parallelism from computational patterns. In *2015 25th*

- *International Conference on Field Programmable Logic and Applications (FPL)*, pages 1–8, Sept 2015.

- [42] A.K. Sujeeth, H. Lee, K.J. Brown, T. Rompf, H. Chafi, M. Wu, AR Atreya, M. Odersky, and K. Olukotun. Optiml: An implicitly parallel domain-specific language for machine learning. In *Proceedings of the International Conference on Machine Learning. Haifa, Israel*, 2011.

- [43] C. Lavin, M. Padilla, J. Lamprecht, P. Lundrigan, B. Nelson, and B. Hutchings. Rapidsmith: Do-it-yourself cad tools for xilinx fpgas. In *Field Programmable Logic and Applications* (*FPL*), 2011 International Conference on, pages 349–355, Sept 2011.

- [44] C. Lavin, B. Nelson, and B. Hutchings. Impact of hard macro size on fpga clock rate and place/route time. In *Field Programmable Logic and Applications (FPL)*, 2013 23rd *International Conference on*, pages 1–6, Sept 2013.

- [45] S. Ma, Z. Aklah, and D. Andrews. A run time interpretation approach for creating custom accelerators. In 2015 25th International Conference on Field Programmable Logic and Applications (FPL), pages 1–4, Sept 2015.

- [46] Sen Ma, Zeyad Aklah, and David Andrews. Just in time assembly of accelerators. In *Proceedings of the 2016 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, Monterey, CA, USA, February 21-23, 2016*, pages 173–178, 2016.

- [47] S. Ma, Z. Aklah, and D. Andrews. Run time interpretation for creating custom accelerators. In 2016 Design, Automation Test in Europe Conference Exhibition (DATE), pages 900–905, March 2016.

- [48] S. Ma and D. Andrews. Breeze computing: A just in time approach for virtualizing fpgas in the cloud. In 2016 International Conference on ReConFigurable Computing and FPGAs (ReConFig), pages 1–6, Dec 2016.

- [49] S. Ma, H. Ding, M. Huang, and D. Andrews. Archborn: an open source tool for automated generation of chip heterogeneous multiprocessor architectures. In *2015 International Conference on ReConFigurable Computing and FPGAs (ReConFig)*, pages 1–6, Dec 2015.

- [50] Sen Ma, Miaoqing Huang, Eugene Cartwright, and David Andrews. Scalable memory hierarchies for embedded manycore systems. In *Proceedings of the 8th International Conference on Reconfigurable Computing: Architectures, Tools and Applications*, ARC'12, pages 151–162, Berlin, Heidelberg, 2012. Springer-Verlag.

- [51] Sen Ma and David Andrews. On energy efficiency and amdahl's law in fpga based chip heterogeneous multiprocessor systems (abstract only). In *Proceedings of the 2014 ACM/SIGDA International Symposium on Field-programmable Gate Arrays*, FPGA '14, pages 253–253, New York, NY, USA, 2014. ACM.

- [52] H. Ding, S. Ma, M. Huang, and D. Andrews. Oogen: An automated generation tool for custom mpsoc architectures based on object-oriented programming methods. In *2016 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW)*, pages 233–240, May 2016.

### Chapter 2

## A Run Time Interpretation Approach For Creating Custom Accelerators

Sen Ma, Zeyad Aklah, and David Andrews

Abstract— The world of software development has the notion of just-in-time compilation, run time binary translation, and language interpretation. These dynamic run time techniques support increased code portability and designer productivity. There are no such equivalences to increase the productivity or portability of creating new hardware components within Field Programmable Gate Arrays (FPGAs). Instead, creating a new hardware component requires hardware design skills and the overhead of running through synthesis, place and route. If a change is made to even a single line of code, the synthesis, place and route steps must be repeated. In this paper we present a new approach that allows hardware accelerators to be built and run using compilation and run time interpretation. Our results show the approach can enable software programmers without any hardware skills to create hardware accelerators at productivity levels consistent with software development and compilation. The same accelerator can be compiled 100× faster than synthesis. Even though the approach is focused on productivity, our observed performance results are promising. Our initial application test cases show the same accelerator written by a software programmer and synthesized through Vivado HLS or written using our DSL and compiled within our approach achieves equivalent performance.

#### 2.1 Introduction

Enabling software developers to apply their skills over Field Programmable Gate Arrays (FPGAs) continues to be an unreached research objective in the reconfigurable computing community. In the past our inability to reach this goal did not greatly impact the adoption of FPGAs within companies that employed hardware and system design engineers. Further the extended time to

market required to program and tune an FPGA to gain peak performance was an acceptable system development cost.

Enabling software developers to apply their skills to FPGAs is now becoming critical as we are witnessing a new and exciting inflection point in their use. FPGAs are now being viewed as viable commercial off the shelf components (COTS) visible to software developers. As an example, Microsoft recently revealed Catapult, a prototype server with FPGAs targeted for use in large data centers to accelerate their Bing search engine. Intel also announced a new compute node that will integrate an FPGA with a Xeon processor. These types of announcements have the potential to accelerate the exposure of FPGAs to software programmers.

This trend is now forcing the research community to address a looming problem for the success of FPGAs within these software domains; there simply are not sufficient numbers of designers with the requisite hardware and architecture design skills needed to handle the work. The United States Bureau of Labor Statistics 2012 report showed approximately 83,000 computer hardware engineers compared to 1.3M software engineers/programmers were employed in the United States [1]. How can the research community address this imbalance?

Our approach allows programmers to compose together a set of highly tuned pre-synthesized bitstreams, or primitives, from within a software development environment. The approach does not replace the need for experienced hardware designers and existing HLS languages and tools. The approach is complementary and allows the large number of programmers to compose bitstreams into new circuits without having to resynthesize. This is achieved by creating a new abstraction layer over the bitstreams that programmers use within their standard software development environments, just as if the bitstreams were more traditional dynamically linkable run time binary executables.

Our results validate that our objective is reachable; different accelerators can be created through compilation and composition, and interpreted at run time. Our initial results show that the same accelerator functionality that takes  $14\sim18$  minutes to synthesize in Vivado can be created

by compiling and linking against an equivalent set of pre-existing bitstreams in seconds. This represents over a  $100 \times$  decrease in development time.

The rest of this paper is organized as follows. The next section provides an overview of our approach. We first show how primitive operations can be combined and compiled. We then introduce a set of platform independent instructions output by our compiler. We also show how the interpreter translates and uses these instructions to configure the primitives within a  $3\times3$  template array of partially reconfigurable slots. Section 5.5 presents our results. Section 6.5 concludes with a discussion on the additional research needed to transition the approach into commercial use.

### 2.2 Approach

Programmers increase their productivity by applying the fundamental software engineering tenets of abstraction, portability and reuse. They do not rewrite each new application from scratch. They take advantage of existing code bases in the form of compilable or dynamically linkable libraries. These libraries represent mechanisms that are invoked within the application code through a set of abstract policies in the form of Application Programmer Interfaces (APIs), system calls, or function prototypes. Can the same approach be applied to help programmers eliminate the need to synthesize an accelerator?

Modern FPGAs support partial reconfiguration. This allows pre-synthesized bitstreams to be downloaded from memory into the FPGA fabric at run time. We take the view that bitstreams should be treated as just another form of pre-compiled executables. The policies of these bitstreams can easily be made available to a programmer through normal software abstractions; APIs or function prototypes.

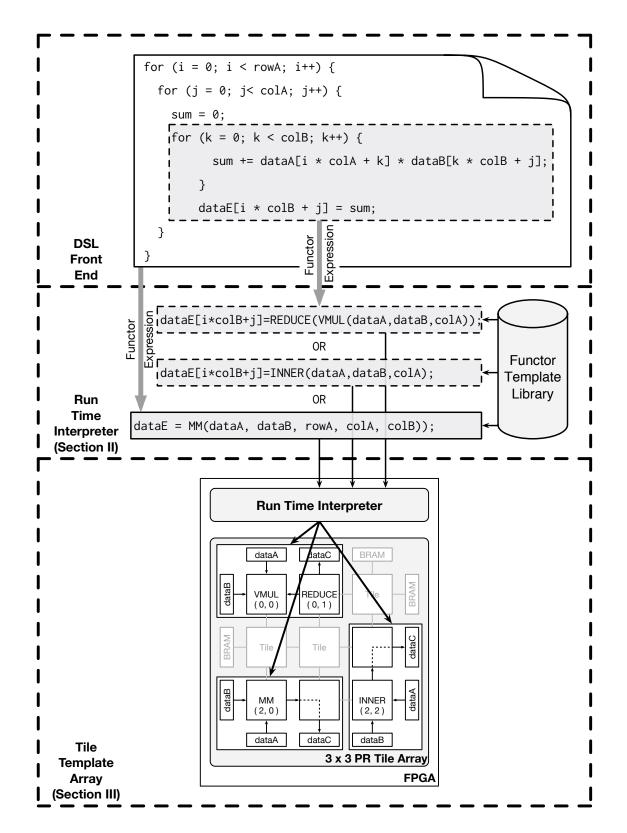

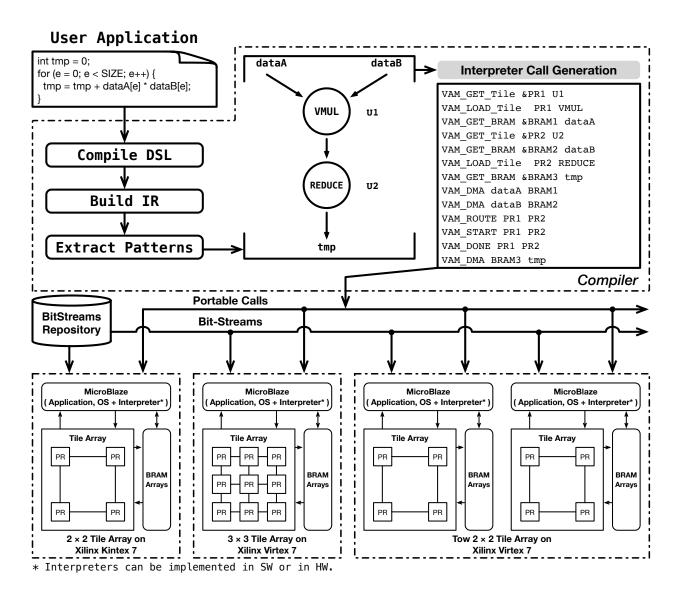

Figure 2.1: Design Flow of Matrix Multiplication Accelerator.

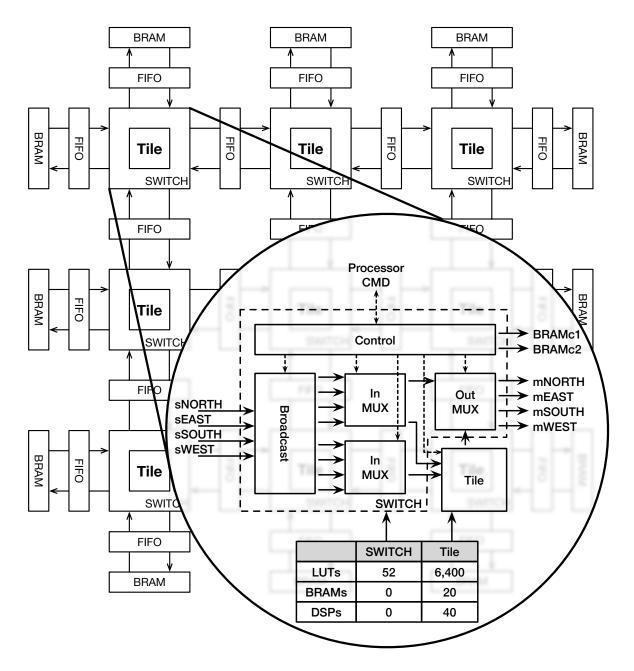

### **2.2.1** Example

Figure 2.1 shows the approach through a simple example. The code in the top of Figure 2.1 implements a simple matrix multiply that a programmer needs to turn into a hardware accelerator. Manipulating the functors can occur within a standard software development environment. We have adopted the Delite [2] framework. Delite is an existing framework developed for creating and compiling Domain Specific Languages (DSLs). The functionality of a functor is created within Delite when the DSL is defined. As part of the DSL design, each functor can be specified in C using an HLS tool, and turned into an optimized bitstream by an experienced hardware designer. It is important to note that this only occurs once during the definition of the DSL. Programmers only use the DSL after it is created. The prototypes are linked later against binaries or bitstreams within the normal compilation process.

### 2.2.2 Run Time Interpreter

Figure 2.1 shows a run time interpreter as part of our approach. We use the interpreter to bring portability and reuse over different organizations of reconfigurable slots. Consider the data flow graph output in Figure 6.6 produced for the inner product example. At this point we could generate code that maps each functor into a physical location for a reconfigurable slot. As an example we could map the *VMUL* functor into the co-ordinates that represent physical slot (0,0), and *REDUCE* into the co-ordinates that represent physical slot (0,1). What would happen if we changed the locations, geometries or numbers of reconfigurable slots? Using the interpreter allows the data flow graph information generated by the back end of our compiler to remain portable, similar to portable Java Byte Code. Since we target the creation of accelerators, we call this language the Virtual Accelerator Machine (VAM) language. Just as a Java Virtual Machine (JVM) provides the run time mechanisms needed to implement the policies defined by the Java Byte Code, our VAM run time interpreter provides the run time executables specific to a particular organization of partially reconfigurable slots. As a more concrete example, we created

Figure 2.2: Compiler Flow and VAM Call Generation.

| Benchmarks                  | Lines of Code (HLS) | Functor Composed Expression                                                                                                                                                                                  |  |

|-----------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Inner Product               | 35                  | dataC=REDUCE( VMUL(dataA, dataB, Size), Size);                                                                                                                                                               |  |

| $M_1 \times V_1$            | 60                  | MatrixC=MM(MatrixA, VectorB, rowA, colA, 1);                                                                                                                                                                 |  |

| $M_1 \times M_2 \times M_3$ | 65                  | MatrixD=MM( MM(MatrixA, MatrixB, rowA, colA, colB), MatrixC, rowA, colB, colC);                                                                                                                              |  |

| Correlation 90              |                     | diff1=SVSUB(dataA, AVG(dataA, Size), Size);<br>diff2=SVSUB(dataB, AVG(dataB, Size), Size);<br>VAR1=REDUCE(VSQR(diff1, Size), SIZE);<br>VAR2=REDUCE(VSQR(diff2, Size), SIZE);<br>Cov=IPR(diff1, diff2, Size); |  |

Table 2.1: Code Complexity

the  $3\times3$  tile array shown in Figure 5.3 as part of our prototype system.

## 2.3 Experimental Results and Analysis

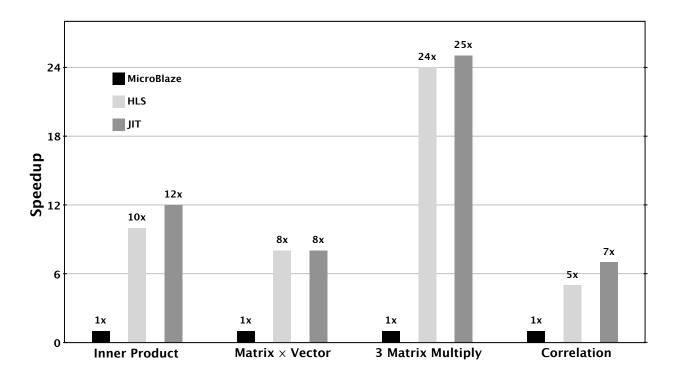

All evaluations were conducted using Vivado 2014.2 with corresponding Vivado HLS tools. All designs were implemented and run on a Xilinx Kintex-7 FPGA. Our test system is shown in Figure 6.6 and consisted of a MicroBlaze, AXI Interconnect, BRAM buffers, DMA, and local BRAM that held our system boot kernel and interpreter executables [3]. Reported times for synthesis and compile are averages of multiple trials. We broke our evaluation into three phases: a feasibility analysis, quantifying productivity, and quantifying performance. The objective of the feasibility analysis was to verify the practicality of the approach.

The seven functors shown in Table 4.2 offered sufficient flexibility to form a variety of test accelerators characteristic of the scientific computing and signal processing domains. The first two functors *VMUL* and *REDUCE* are familiar programming patterns. The *SVSUB*, *VSQR*, and *AVG* functors were created to form filtering patterns from signal processing. The *IPR* functor computes the inner product between two vectors. The *MM* was created to support

multidimensional matrix operations from scientific computing as well as signal processing. Each functor was hand coded in C and synthesized using Vivado HLS and Vivado to create partially reconfigurable bitstreams. The functor prototypes and their bitstreams were placed in a library.

Table 4.2 shows how the functors were composed to implement the four benchmarks. The first benchmark showed how the two simple functors, *REDUCE* and *VMUL*, can be composed to create an inner product. The third benchmark showed how a three dimensional matrix multiply can be formed by composing two *MM* functors. The fourth benchmark showed how a series of five functors could be composed to form a correlation function. In all cases the functors were composed within our DSL, and all VAM interpreter calls automatically generated. The produced run time results were compared to software versions running on a workstation. All benchmarks ran successfully.

#### 2.3.1 Productivity Analysis

Table 4.2 lists the number of C source lines written to code a single accelerator version of each benchmark. The lines of C source includes code required to interface and control the accelerator. Intuitively eliminating the need to write low level interface code will increase productivity. The thirty five lines of C code required for the inner product is replaced by composing the two *REDUCE* and *VMUL* functors. Ninety lines of C code for the correlation was replaced by five functors. We did not attempt to measure the time it took to code each benchmark accelerator. We simply use the number of source lines as a quantifying metric.

Table 3.3 quantifies productivity by comparing synthesis versus compilation times for each benchmark. Each benchmark was compiled in under 5s. The actual time to compile just the functors was probably under a second. The reported times include additional compilation and linking that occurs within our automated system build toolchain. Our results show that compilation occurred between  $170\times$  to  $214\times$  faster than synthesis. Just this difference alone in a development flow has significant implications on programmer productivity. Under synthesis, a

Figure 2.3:  $3 \times 3$  Tile Array and Interconnect Network.

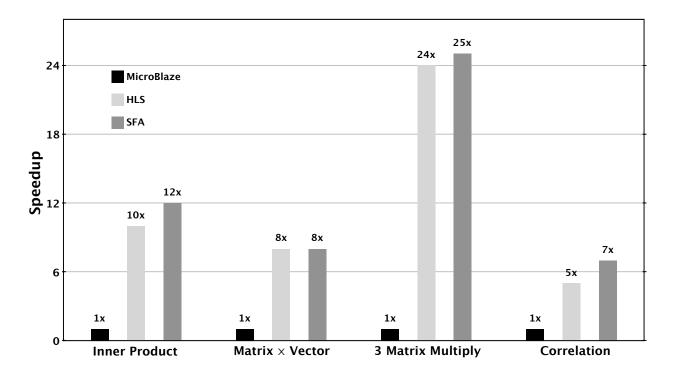

Figure 2.4: Speedup of Benchmarks.

software designer would need to wait an average of 15 minutes before the bitstreams could be generated and then tested in a running system. This equates to being able to make only four changes per hour. In comparison, a programmer using our approach can make and observe approximately 180 changes per hour. How such a level of productivity would result in rapid fix bugs is intuitive. Importantly the approach allows the programmer to quickly and easily experiment with different accelerators running within the real system.

Similar to software implementations of run time interpreters, our VAM interpreter introduced overhead. We measured an overhead of between  $64\mu s$  (for the inner product) to  $650\mu s$  (for the correlation) for the interpreter to select tiles, and route functors. The overheard scaled fairly linearly based on the number of tiles that were used. Although we thought it fair to call this overhead out, it should be viewed similar to the startup overhead that would be incurred once during the creation of a thread in a multithreaded operating system. After the functors have been placed and routed, this overhead is no longer seen. To be complete, there is also overhead associated with transferring bitstreams into the tiles. This overhead would also be present for

| Benchmarks                  | SFA Compilation<br>Overhead (s) | HLS Synthesis & PAR Overhead (s) | Productivity<br>Improvement |

|-----------------------------|---------------------------------|----------------------------------|-----------------------------|

| Inner Product               | <u>≤</u> 5                      | 865                              | 173×                        |

| $M_1 \times V_1$            | <u>≤</u> 5                      | 889                              | 178×                        |

| $M_1 \times M_2 \times M_3$ | <u>≤</u> 5                      | 1034                             | 207×                        |

| Correlation                 | <u>≤</u> 5                      | 1068                             | 214×                        |

Table 2.2: productivity

transferring the bitstreams of the synthesized custom accelerator. In both cases the overhead is approximately equal and provides no differentiation between this approach and a traditional synthesis approach.

#### 2.3.2 Performance Analysis

Lastly we wanted to observe if an accelerator created by composing bitstreams would suffer some measure of degraded performance compared to synthesizing a combined single bitstream version. Clearly the performance any synthesized accelerator or primitive is dependent on many different factors, including how the code is structured, the time taken to optimize the code, the designers hardware design skills. The fundamental question we sought to answer was at this stage of development would performance be degraded sufficiently to negate the approach. Figure 3.6 shows our results. We were intrigued to observe that our approach achieved speedups that were as good or better than the speedups of the synthesized accelerator. While the results are promising we do not draw any conclusions on performance based on just these prototype benchmarks. For this study we conclude that the results simply do not negate the validity of the approach. Clearly, more DSLs and more applications need to be evaluated before any real claim on performance trends can be made.

#### 2.4 Related work

The work reported in this paper benefits from and contributes to the large body of research in programming languages and models, virtualization of hw/sw resources, operating systems, and partial reconfiguration. The use of Domain Specific Languages to generate accelerators is discussed in [4, 5, 6].

Using a DSL allows additional higher level domain specific optimizations to be made, such as fusing and transforming individual programming patterns into a more efficient representation. This optimized representation can then be run through synthesis. Our approach exploits some of the benefits of using tuned programming patterns, but differs by pre-synthesizing the patterns into functors that can be linked. We also retarget the back end to generate platform independent interpreter calls and not a synthesis tool. Research in this area roughly follows along three lines: improve and optimize the algorithms, minimize the work fed into the synthesis tool, or eliminate synthesis from the design flow by moving it into the run time system. We share commonalities with the second and third approaches. Work by Nelson [7] represents an interesting approach to minimize the work fed into the synthesis tool. Athanas combined this idea with partial reconfiguration to rapidly assemble software defined radios [8]. Lysecky and Vahid [9] explored moving synthesis from design time to run time. In their Warp Processing work, they targeted synthesizing the body of a loop while it was running. Similarly, Davor et al. [10] proposed a synthesis-free JIT approach to dynamically accelerate hot segments in a program using off line synthesized VDR units.

Our approach shares the same philosophy of creating the equivalent of macro IP components. However our approach eliminates the need to do additional routing within the physical control layer of the FPGA within the synthesis tool.

#### 2.5 Conclusion

In this work, we presented a new approach that allows programmers to use standard software development tools and enjoy software levels of productivity when creating new hardware accelerators. The main contribution of this work is the elimination of synthesis from the path of a programmers design flow. This will greatly facilitate the use of FPGAs within our software dominated information technology sector. We validated this new approach by prototyping an end to end system running on a test system configured as a  $3\times3$  array of tiles. The end to end system included a prototype compiler that allowed functors to be composed, type checked, and generate machine independent interpreter calls. We implemented a run time interpreter that implemented these calls on our  $3\times3$  tile array. Our results validated the feasibility of the approach. We showed how equivalent accelerator functionality could be represented by composition, compilation and run time interpretation of functors thereby eliminating the need to pass through synthesis.

#### References

- [1] http://www.bls.gov/ooh/Computer-and Information-Technology/. Occupational Outlook Handbook.

- [2] K.J. Brown, A.K. Sujeeth, Hyouk Joong Lee, T. Rompf, H. Chafi, M. Odersky, and K. Olukotun. A heterogeneous parallel framework for domain-specific languages. In *Parallel Architectures and Compilation Techniques (PACT), 2011 International Conference on*, pages 89–100, Oct 2011.

- [3] Sen Ma, Miaoqing Huang, and D. Andrews. Developing application-specific multiprocessor platforms on fpgas. In *Reconfigurable Computing and FPGAs (ReConFig)*, 2012 *International Conference on*, pages 1–6, Dec 2012.

- [4] Rishiyur Nikhil. Bluespec system verilog: efficient, correct rtl from high level specifications. In *Formal Methods and Models for Co-Design, 2004. MEMOCODE '04. Proceedings. Second ACM and IEEE International Conference on*, pages 69–70, June 2004.

- [5] N. George, Hyoukjoong Lee, D. Novo, T. Rompf, K.J. Brown, A.K. Sujeeth, M. Odersky, K. Olukotun, and P. Ienne. Hardware system synthesis from domain-specific languages. In *Field Programmable Logic and Applications (FPL), 2014 24th International Conference on*, pages 1–8, Sept 2014.

- [6] O. Reiche, M. Schmid, F. Hannig, R. Membarth, and J. Teich. Code generation from a domain-specific language for c-based hls of hardware accelerators. In *Hardware/Software Codesign and System Synthesis (CODES+ISSS)*, 2014 International Conference on, pages 1–10, Oct 2014.

- [7] C. Lavin, B. Nelson, and B. Hutchings. Impact of hard macro size on fpga clock rate and place/route time. In *Field Programmable Logic and Applications (FPL)*, 2013 23rd *International Conference on*, pages 1–6, Sept 2013.

- [8] A.B. MacKenzie, J.H. Reed, P. Athanas, C.W. Bostian, R.Michael Buehrer, L.A. DaSilva, S.W. Ellingson, Y.T. Hou, M. Hsiao, Jung-Min Park, C. Patterson, S. Raman, and C. da Silva. Cognitive radio and networking research at virginia tech. *Proceedings of the IEEE*, 97(4):660–688, April 2009.

- [9] Roman Lysecky, Greg Stitt, and Frank Vahid. Warp processors. *ACM Transactions on Design Automation of Electronic Systems (TODAES*, 11:659–681, 2006.

- [10] D. Capalija and T.S. Abdelrahman. Towards synthesis-free jit compilation to commodity fpgas. In *Field-Programmable Custom Computing Machines (FCCM)*, 2011 IEEE 19th Annual International Symposium on, pages 202–205, May 2011.

## Chapter 3

## **Just In Time Assembly of Accelerators**

### Sen Ma, Zeyad Aklah, and David Andrews

Abstract— Despite the significant advancements that have been made in High Level Synthesis, the reconfigurable computing community has failed at getting programmers to use Field Programmable Gate Arrays (FPGAs). Existing barriers that prevent programmers from using FPGAs include the need to work within vendor specific CAD tools, knowledge of hardware programming models, and the requirement to pass each design through synthesis, place and route. In this paper we present a new approach that takes these barriers out of the design flows for programmers. Synthesis is eliminated from the application programmers path by becoming part of the initial coding process when creating the programming patterns that define a Domain Specific Language. Programmers see no difference between creating software or hardware functionality when using the DSL. A run time interpreter is introduced that assembles hardware accelerators within a configurable tile array of partially reconfigurable slots at run time. Initial results show the approach allows hardware accelerators to be compiled 100× faster compared to the time required to synthesize the same functionality. Initial performance results further show a compilation/interpretation approach can achieve approximately equivalent performance for matrix operations and filtering compared to synthesizing a custom accelerator.

#### 3.1 Introduction

Just In Time (JIT) compilation and run time interpretation has been effective at delivering portability within the software world. In this work we investigate if the same JIT run time interpretation philosophy can be used to enable programmers, not hardware designers, to assemble hardware accelerators at run time on todays FPGAs.

This is no small challenge. Creating such a capability requires rethinking what is synthesized, when synthesis should occur, and how certain steps within the place and route sequence can be moved into the run time system.

Synthesis cannot be totally eliminated, but can be moved out of a programmer's compilation path. Domain Specific Languages (DSLs) provide a path forward [1, 2, 3]. Our assertion is that synthesis can be taken out of the application developers path if it is made part of the standard coding process when the Domain Specific Language (DSL) is created. This is before an application programmer attempts to combine and compile individual programming patterns into an application.

Individual programming pattern bitstreams can be made available as executable library routines. These library routines can be symbolically referred to during compilation as yet another form of a dynamically linked run time executable. Thus the bitstreams are treated no differently during compilation as traditional libraries of binary executables. The place and route steps that traditionally occur when bitstreams are combined together before synthesis can be moved into the run time system.

Java compilers produce platform independent Java bytecodes that are translated into native machine code during run time by the Java Virtual Machine (JVM). The symbolic links to the individual bitstreams can be output from a compiler as pointers to the hardware module equivalents of the native methods. They are just spatial instead of temporal representations.

The hardware native methods (bitstreams) then need to be substituted in place of the symbolic links at run time. We define a new run time interpreter to perform the equivalent function of the JVM. Instead of substituting byte codes with native machine code, the run time interpreter will substitute the symbolic links with the relocatable hardware modules.

The interpreter needs spaces within the FPGA to place the hardware modules and a programmable interconnect that can route data between the modules. FPGAs already provide the structure to support this through partial reconfiguration [4]. We create a network overlay with

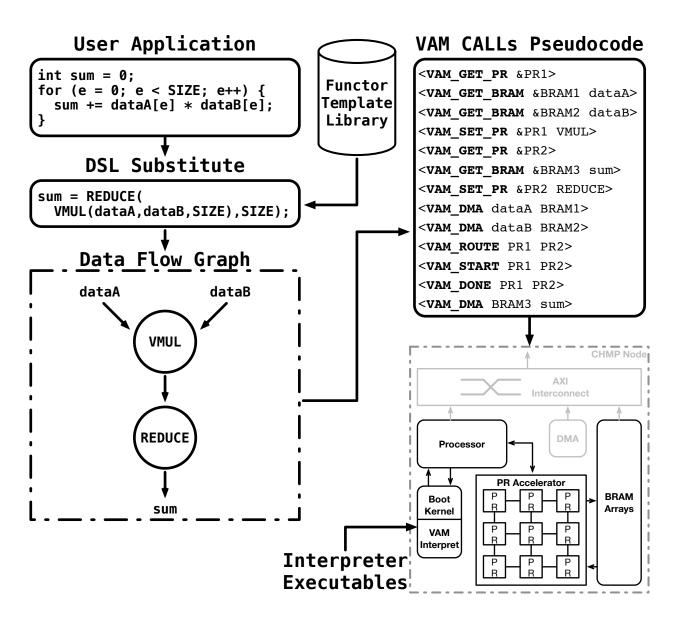

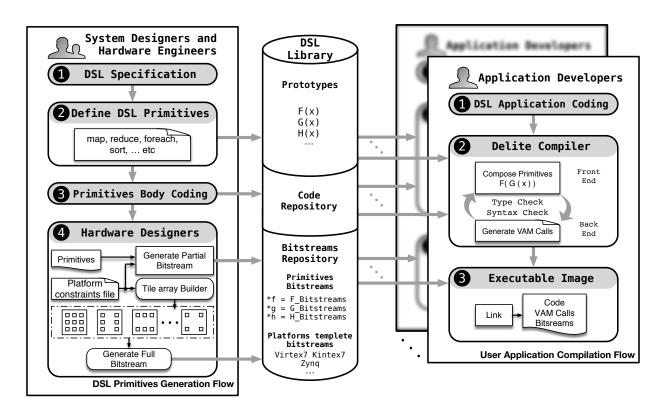

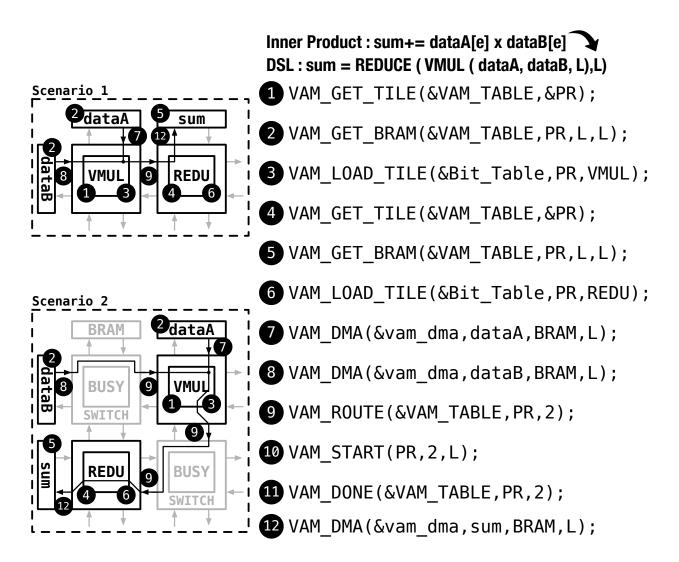

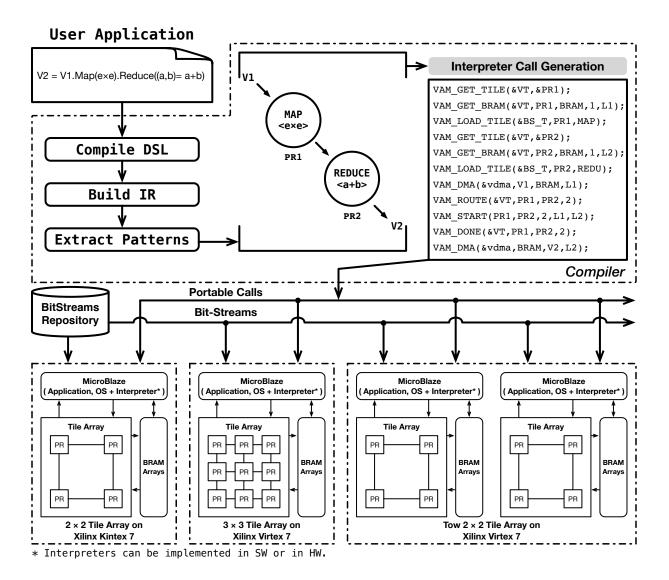

Figure 3.1: Design Flow.

programmable interconnects. Partial reconfiguration regions are provided into which the interpreter can place the modules and route them together at run time.

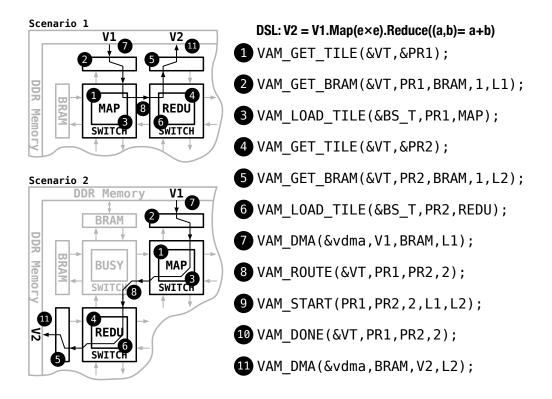

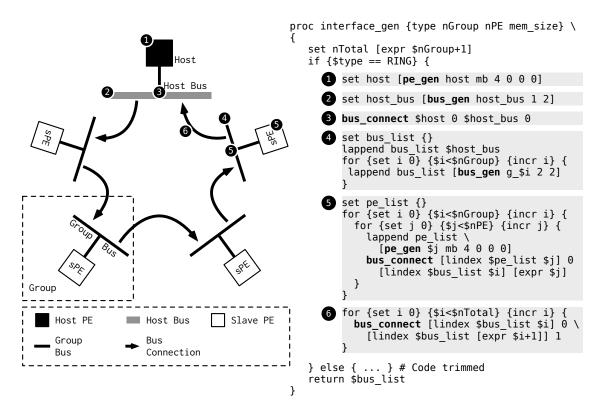

Figure 3.1 shows our end to end design flow. The left side shows what occurs by a system programmer when creating a Domain Specific Language (DSL) for the application programmers. During the normal coding process that occurs when programming patterns are created, we add the additional step of synthesizing each individual pattern into a bitstream. This is discussed in section 3.3. The bottom left of Figure 3.1 shows the introduction of a new type of overlay network. This overlay is created once when the programming patterns are coded and synthesized. The new overlay is discussed in section 3.2. The programming patterns, bitstreams, and overlay are placed into libraries shown in the middle of Figure 3.1 and can be accessed by all application programmers.

The application programmers use the flow on the right in Figure 3.1 to create their applications. They work with standard software DSL primitives just as if they are coding their

application for a traditional software implementation. However when the programmer composes DSL primitives that have bitstream representations, the compiler inserts symbolic links to the bitstreams and builds a data flow graph representation of how the programming patterns are composed to represent the accelerator.

The compiler outputs a series of interpreter instructions that are used by an interpreter to assemble the bitstreams within the overlay and set the data connections. This is discuss in section 4.3.

#### 3.1.1 Contributions

The main contributions of this work are:

- *PR Tile Overlay* A new overlay that uses partial reconfiguration tiles within a 2D Array and flexible word width switch boxes. The overlay represents the framework within which the run time system assembles accelerators. We provide a scripting tool to automatically create different configurations of the overlay for a DSL and FPGA.

- Platform Independent Interpreter Language A set of platform independent interpreter calls

used by an interpreter to assemble accelerators on different configurations of the PR tile

overlay at run time.

- *Run Time Interpreter* We created a C implementation of the interpreter. The interpreter dynamically places and routes the programming patterns within different configurations of the overlay. The interpreter calls are compiled and linked as sys\_calls within a pthreads compliant multithreaded programming model middleware library.

- Case Studies and Evaluation Case studies showing a complete end to end capability. Case studies show how accelerators are formed from the programming patterns of a DSL, compiled, JIT assembled and run within different overlays. We show the portability of the approach by running the same compiled accelerator in different overlays, including single

and multiprocessor systems on chip architectures on Virtex7 and Kintex7 FPGAs. Run time performance and area overhead comparison studies are provided that compare the approach to traditional synthesis flows.

#### 3.2 Intermediate Fabric

Commercial off-the-shelf FPGAs have served and will continue to serve as the defacto component for reconfigurable computing research. This is not because they are ideal, in fact they are far from it. Course Grained Reconfigurable Arrays (CGRAs) have been proposed as alternatives to FPGA fabrics for reconfigurable computing [5]. CGRAs replace Lookup tables (LUTs) and Flop Flops with programmable Arithmetic Logic Units (ALUs) and word width interconnects as compilation targets. CGRA structures promise to close the semantic gap between high level languages and hardware and change design flows from synthesis to compilation [6]. Even though interest in CGRAs remains high no devices are available.

Intermediate Fabrics, or overlays have been proposed that allow CGRA type structures [7] as well as more higher level computational components such as vector processors [8] to be embedded within FPGAs. The potential advantage of such overlays is that circuits and hardware acceleration can be achieved through compilation instead of synthesis on existing FPGAs. Common approaches for enabling CGRAs on an FPGA are to replace LUTs and Flip Flops with small programmable computational units such as ALUs as the compilation target. The ALUs are embedded within a network of switch boxes and channels.

The interconnect structures are defined to support wider word widths instead of bit level interconnections. The general approach introduces some overhead inefficiencies associated with need to provide additional resources to form the overlay, routing delays between the computational units, and limitations on the granularity of parallelism that can be exploited. New approaches to addressing overhead and latency issues continue to be investigated [9].

We defined a hybrid type of overlay to support JITing bitstreams.

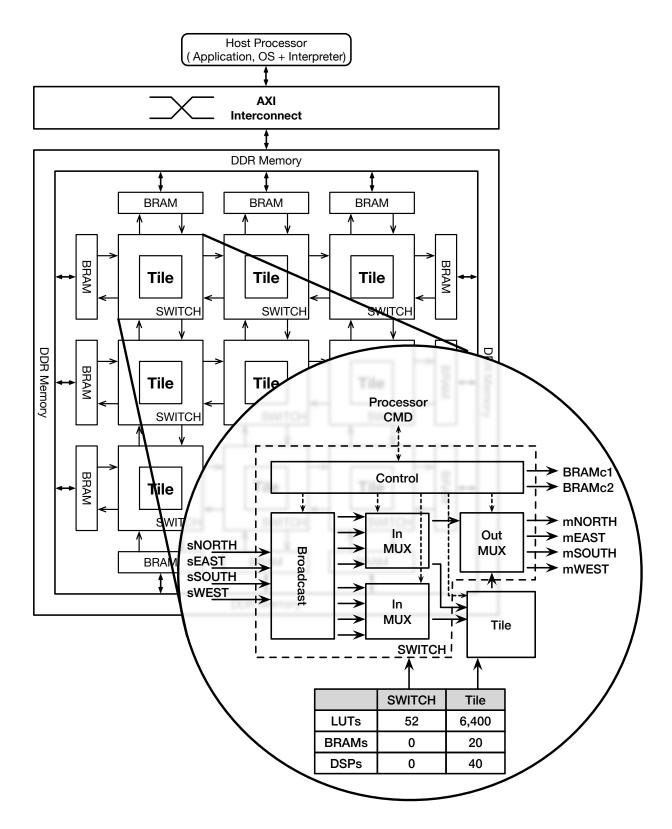

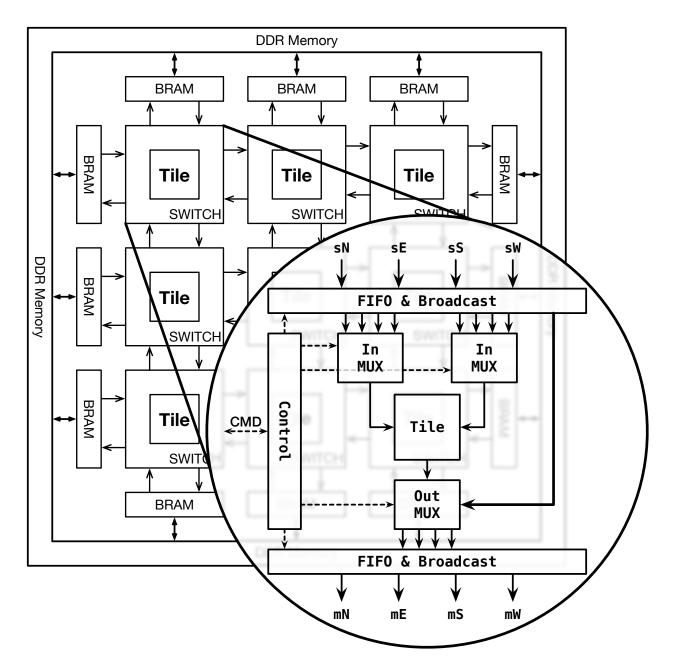

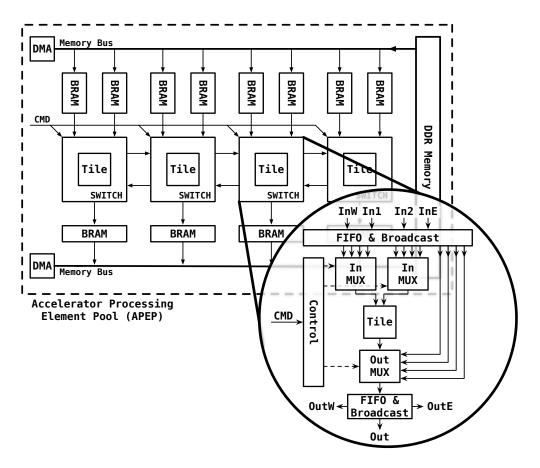

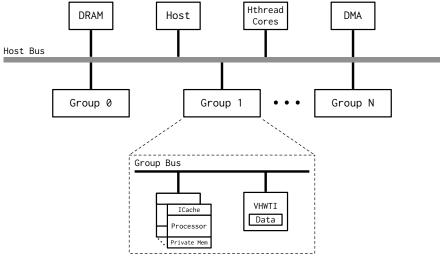

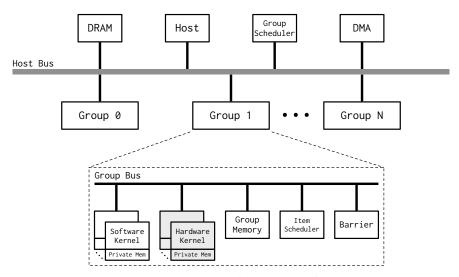

Our overlay includes a nearest neighbor programmable word width interconnect similar to traditional CGRA type overlays. Different from traditional CGRA overlays, we expose the lookup tables and flip flops of the FPGA as partially reconfigurable tiles instead of abstracting them into programmable computational units. This combination of pre-formed interconnects and partial reconfiguration regions allows the bitstreams for the programming patterns to be downloaded at run time into the intermediate fabric. Figure 5.3 shows the structure of the hybrid overlay. The basic structure is a 2D array of partial reconfiguration tiles and programmable switches that are connected as a nearest neighbor interconnect network.

#### **3.2.1 PR Tiles**

The specific  $3\times3$  array configuration shown in Figure 5.3 was constructed of partial reconfiguration tiles sized at 9,600 LUTS, 360KB BRAM, and 80 DSPs. This particular configuration was sized to hold the largest bitstream generated from our test DSL. The exact size of the tiles is variable and can be set when the DSL is first created.

The number of the tiles is derived based on the size of the tiles and the number of resources available on a target FPGA logic family.

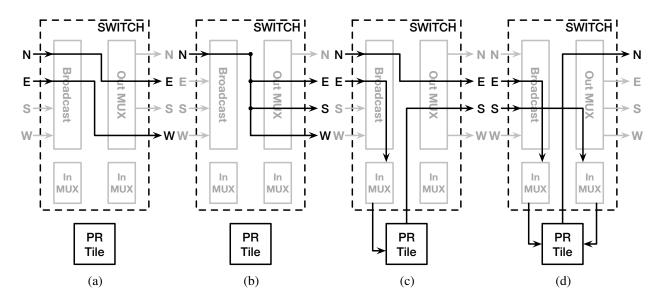

#### 3.2.2 Programmable Switch

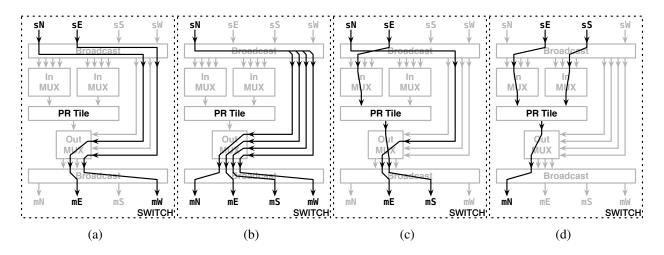

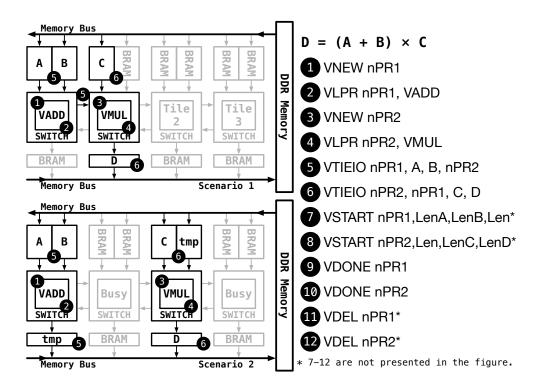

Figure 4.4 provides an exploded view of a switch. Figure 4.4 shows the types of routing patterns that can be programmed into switch. The routing patterns were defined to enable each switch to direct inputs and outputs through the tile, as well as serving as a pass through for routes between distant tiles.

Routes can be set statically or dynamically. Dynamic settings can be used for allowing the switch to support different time varying routing needs such as when multiple accelerators are

Figure 3.2:  $3 \times 3$  Tile Array and Interconnect Network.

Figure 3.3: Switch Routing.

resident within the overlay. Each switch may serve as a pass through for one accelerator, and then source and synch data for a tile that is part of a different accelerator.

### 3.2.3 Local Memory

The boundary cells in the overlay include connections to blocks of local memories (BRAMs).

These BRAMS can be used as addressable local memories or as FIFO data buffers for streaming data.

Block data transfers use DMA (not shown) between the BRAMs and Global DRAM memory. The BRAMs are placed within the global address map of the system, allowing any processor or bus master device to transfer data into and out of a local memory. The BRAMS have buffer full/empty handshaking signals that are connected through the switches to enable processing to be dynamically triggered.

## **3.3** The Programmers Perspective

Domain Specific Languages (DSLs) are common within software development flows and offer a reduced set of programming patterns tailored for a particular application domain.

An advantage of a DSL approach is that domain s pecific optimizations can be applied to the programming patterns before they are translated into lower level intermediate representations.

The programming patterns themselves hide complexity and allow the compiler and run time system to better decompose and map the computations across different configurations of architectures and computational resources. For these reasons, DSLs are gaining interest within the general purpose computing domain as a approach to increase performance and productivity for heterogeneous multiprocessors [2].

Our approach deviates from the current approaches that combine programming patterns prior to synthesis. When the programming patterns that define a DSL are first created, there is no reason why they cannot be synthesized before they are combined. The individual bitstream versions of the programming patterns can be placed within a corresponding library of linkable executables. The compiler can then refer to executables using symbolic links just like dynamically linked software routines.

This view presents a subtle but important difference from today's current approaches. Consider the differences in flows, design skills and development time needed to create the two separate hardware accelerators  $acc_1$  and  $acc_2$  using the following three generic functions f(x), g(y), h(z).  $acc_1 := f(g(h(z)))$ ;  $acc_2 := g(g(h(z)))$ ;